United States District Court, D. New Jersey.

GENERAL ELECTRIC COMPANY, Plaintiff. v. NINTENDO COMPANY, LTD. and Nintendo of America, Inc, Defendants.

Oct. 7, 1997.

#### As Amended Nov. 7, 1997.

Owner of patents relating to electronic circuitry used in connection with television systems brought infringement action against manufacturer of video game systems. Video game manufacturer moved for summary judgment. The District Court, Wolin, J., held that: (1) patent for video record player switching system was invalid as anticipated, and (2) patents were not infringed.

Defendant's motion for summary judgment granted.

4,282,549, 4,709,256. Cited.

Lisa M. Walsh, Tricia Bevelock O'Reilly, Marc D. Haefner, Connell, Foley & Geiser, Roseland, NJ and Thomas V. Heyman, Joseph D. Pollack, Blaney Harper, Douglas I. Lewis, Jones, Day, Reavis & Pogue, New York, NY, for Plaintiff.

John J. Kirby, Jr, Thomas G. Gallatin, Jr., Robert J. Gunther, Jr, John T. Brennan, James S. Blank, Latham & Watkins, New York, NY, Michael Chertoff, Latham & Watkins, Newark, NJ, (Charles P. Baker, Robert H. Fischer, Michael P. Sandonato, Fitzpatrick, Cella, Harper & Scinto, New York, NY, of counsel) for Defendants.

#### **OPINION**

WOLIN, District Judge.

#### TABLE OF CONTENTS

| I. | LEC | GAL PRECEPTS                                       | Page<br>518 |  |

|----|-----|----------------------------------------------------|-------------|--|

|    | A.  | Summary Judgment Standard                          | 518         |  |

|    | B.  | Summary Judgment in Patent Infringement Litigation | 518         |  |

|    | C.  | Patent Infringement                                | 519         |  |

|     |                                    | 1.         | Claim Construction                                                                                                                                                         | 519 |

|-----|------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     |                                    | 2.         | Literal Infringement                                                                                                                                                       | 519 |

|     |                                    | 3.         | Doctrine of Equivalents                                                                                                                                                    | 519 |

|     | D.                                 | Inva       | lidity by Anticipation                                                                                                                                                     | 520 |

| II. | UNITED STATES PATENT NO. 4,097,899 |            |                                                                                                                                                                            |     |

|     | A.                                 | Background |                                                                                                                                                                            | 520 |

|     |                                    | 1.         | Function and Structure of the '899 Patent                                                                                                                                  | 522 |

|     |                                    | 2.         | Nintendo's Denial of Infringement and Claim of Invalidity                                                                                                                  | 522 |

|     |                                    |            | a. Nintendo's RF Switch.                                                                                                                                                   | 522 |

|     |                                    |            | <ul> <li>b. Nintendo's Arguments in Support of the Lack of Equivalency Between the<br/>Function and Structure of the '899 Patent as Compared to the '478 Patent</li> </ul> | 523 |

|     |                                    |            | c. Nintendo's Invalidity Claim: Anticipation of the '899 Patent                                                                                                            | 523 |

|     |                                    | 3.         | GE's Reply to Nintendo's Non-Infringement and Claim Construction Analysis                                                                                                  | 524 |

|     |                                    | 4.         | Expert Testimony                                                                                                                                                           | 524 |

|     |                                    |            | a. Kurt Wallace for GE                                                                                                                                                     | 524 |

|     |                                    |            | b. James Roberge for Nintendo                                                                                                                                              | 524 |

|     |                                    |            | c. Katsuya Nakagawa for Nintendo                                                                                                                                           | 524 |

|     | В.                                 | Dise       | cussion                                                                                                                                                                    | 529 |

|     |                                    | 1.         | Non-infringement of Claim 12 of the '899 Patent                                                                                                                            | 529 |

|     |                                    |            | a. Literal Infringement                                                                                                                                                    | 529 |

|     |                                    |            | b. Infringement Under the Doctrine of Equivalents                                                                                                                          | 530 |

|     |                                    | 2.         | Non-infringement of Claims 13 and 14 of the '899 Patent                                                                                                                    | 532 |

|      |    | 3.   | Claims 12-14 of the '899 Patent Are Invalid                  | 532 |

|------|----|------|--------------------------------------------------------------|-----|

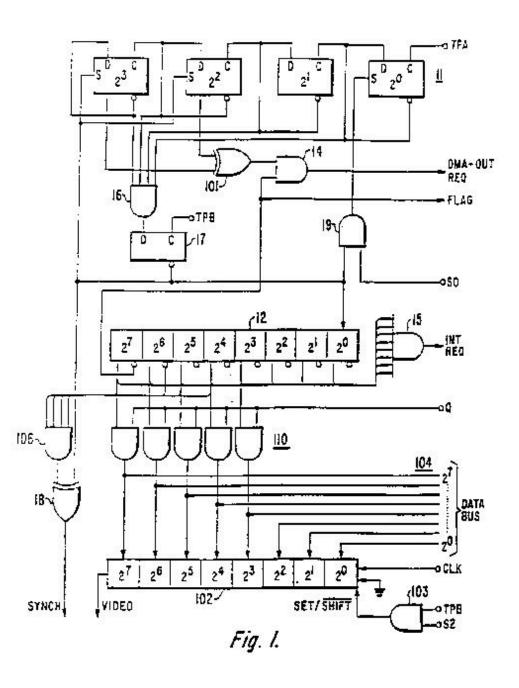

| III. | UN | ITED | STATES PATENT NO. 4,169,659                                  | 534 |

|      | A. | Bac  | kground                                                      | 534 |

|      |    | 1.   | Sync Generators                                              | 534 |

|      |    | 2.   | The '659 Patent                                              | 536 |

|      |    |      | a. Drive Signals                                             | 537 |

|      |    |      | b. Vertical Counter Clocked by Signal Advanced in Phase      | 537 |

|      |    | 3.   | Nintendo's Denial of Infringement                            | 538 |

|      |    |      | a. Nintendo's SNES Sync Generator                            | 538 |

|      |    |      | b. Nintendo's Arguments in Support of Non-Infringement Claim | 539 |

|      |    | 4.   | GE's Reply to Nintendo's Non-Infringement Analysis           | 541 |

|      |    |      | a. Drive Signals                                             | 541 |

|      |    |      | b. Vertical Counter Clocked by Signal Advanced in Phase      | 542 |

|      |    |      | c. Doctrine of Equivalents                                   | 542 |

|      |    | 5.   | Expert Testimony                                             | 542 |

|      |    |      | a. Steven Mayer for Nintendo                                 | 542 |

|      |    |      | b. Bernard Lechner for GE                                    | 545 |

|      | B. | Disc | cussion                                                      | 546 |

|      |    | 1.   | Non-infringement of Claim 1 of the '659 Patent               | 546 |

|      |    |      | a. Literal Infringement                                      | 546 |

|      |    |      | (1) Drive Signals                                            | 546 |

|     |    |      | (2) Vertical Counter Clocked by Signal Advanced in Phase     | 549 |

|-----|----|------|--------------------------------------------------------------|-----|

|     |    |      | b. Infringement Under the Doctrine of Equivalents            | 550 |

|     |    | 2.   | Non-infringement of Claims 3, 4, 5 and 13 of '659 Patent     | 551 |

| IV. | UN | ITED | D STATES PATENT NO. 4,270,125                                | 551 |

|     | A. | Bac  | kground                                                      | 551 |

|     |    | 1.   | Display Systems                                              | 551 |

|     |    | 2.   | The '125 Patent                                              | 552 |

|     |    |      | a. Data Transfer Technique                                   | 553 |

|     |    |      | b. Refresh Technique                                         | 554 |

|     |    |      | c. Gating Means                                              | 554 |

|     |    | 3.   | Nintendo's Denial of Infringement                            | 555 |

|     |    |      | a. Nintendo's SNES and Gameboy Systems                       | 555 |

|     |    |      | b. Nintendo's Arguments in Support of Non-Infringement Claim | 557 |

|     |    |      | (1) Data Transfer Technique                                  | 557 |

|     |    |      | (2) Refresh Technique                                        | 558 |

|     |    |      | (3) Gating Means                                             | 559 |

|     |    | 4.   | GE's Reply to Nintendo's Non-Infringement Analysis           | 559 |

|     |    |      | a. Data Transfer Technique                                   | 559 |

|     |    |      | b. Refresh Technique                                         | 560 |

|     |    |      | c. Gating Means                                              | 561 |

|     |    | 5.   | Expert Testimony                                             | 561 |

|    |               | a.                   | Steven Mayer for Nintendo                  | 561 |

|----|---------------|----------------------|--------------------------------------------|-----|

|    |               | b.                   | Robert Pelovitz for GE                     | 564 |

|    |               | c.                   | Joel Snyder for GE                         | 565 |

| B. | B. Discussion |                      |                                            | 565 |

|    | 1.            | Literal Infringement |                                            | 565 |

|    |               | a.                   | Data Transfer Technique                    | 565 |

|    |               | b.                   | Refresh Technique                          | 567 |

|    |               | c.                   | Gating Means                               | 568 |

|    | 2.            | Infr                 | ingement Under the Doctrine of Equivalents | 569 |

570

# V. CONCLUSION

Before the Court today are two behemoths of the television electronics industry-General Electric Company ("GE") and Nintendo Company, Ltd. ("Nintendo"). FN1 Their respective products, and ones like them, are embedded in the core of the visual society that we have become. Indeed, one would be hard pressed to find someone who does not have a GE product in his home or a person who has never watched a program on a GE television. Likewise, Nintendo products are a lightning rod of interest that electrify the realm of personal entertainment and it is rare to find an individual, at least one of a less-distinguished age than the Court, who has never been challenged by one of the ever-growing number of video games. Ironically, there are probably thousands of homes in which Nintendo video game systems are harmoniously connected to GE televisions. Such harmony is rendered atonal, however, the moment litigation begins.

FN1. Nintendo of America, Inc. is also a named defendant and is, collectively with Nintendo Company, Ltd., referred to as "Nintendo."

GE initiated this action alleging that certain of Nintendo's video game products infringed three separate patents owned by GE. FN2 The patents (and respective claims) under consideration are: United States Patent No. 4,097,899 (Claims 12-14), United States Patent No. 4,169,659 (Claims 1, 3, 4, 5 and 13) and United States Patent No. 4,270,125 (Claim 1). Each of the patents generally relates to electronic circuitry used in connection with television systems. FN3

FN2. Each of the patents at issue here was originally assigned to RCA Corporation ("RCA") and later acquired by GE as part of an asset purchase. *See*, *e.g.*, Nintendo's '899 Br. at 2 n.3.

FN3. Due to the complexity of the subject matter of the patents, the parties submitted expert certifications with respect to each motion. These certifications were intended, in part, to educate the Court regarding the electronic structure of the patents (and allegedly infringing devices) and the relevance and function of the

patents in the world of television electronics. Each expert certification includes as an exhibit a CD-ROM tutorial discussing the patent and summarizing the opinion of the respective expert. Each CD-ROM runs approximately 45-60 minutes. While generally reiterating the information found in the written expert certifications, the CD-ROMs were of significant use to the Court; as noted, the world in the 1990s is a visual society, of which the Court is a member. The parties and their coursel are to be commended for the high quality of both their written and audio/visual presentations.

Through its present applications for summary judgment, Nintendo seeks a declaration of non-infringement in regard to each of GE's patents. With respect to patent No. 4,097,899, Nintendo alternatively asserts that the patent is invalid by anticipation. FN4 As set out below, the Court has separately analyzed and discussed each of the patents under a single statement of the applicable law. The order of consideration of the patents is random. For the reasons stated herein, the Court will grant Nintendo's motions for summary judgment on each of the three patents.

FN4. Nintendo initially asserted that patent No. 4,270,125 was invalid. In the course of briefing this motion, however, Nintendo withdrew that argument. Nintendo reserved the right to assert invalidity as a defense at trial.

# **I. LEGAL PRECEPTS**

# A. Summary Judgment Standard

Rule 56(c) of the Federal Rules of Civil Procedure provides that summary judgment shall be granted if "the pleadings, depositions, answers to interrogatories, and admissions on file, together with the affidavits, if any, show that there is no genuine issue as to any material fact and that the moving party is entitled to a judgment as a matter of law." *See* Hersh v. Allen Prods. Co., 789 F.2d 230, 232 (3d Cir.1986). A dispute involving a material fact is "genuine" only "if the evidence is such that a reasonable jury could return a verdict for the nonmoving party." Anderson v. Liberty Lobby, Inc., 477 U.S. 242, 248, 106 S.Ct. 2505, 2510, 91 L.Ed.2d 202 (1986). The Supreme Court also observed that "[o]nly disputes over facts that might affect the outcome of the suit under governing law will properly preclude an entry of summary judgment." *Id.; see also* Ness v. Marshall, 660 F.2d 517, 519 (3d Cir.1981) (role of district court is to determine whether genuine issue of material fact exists).

Furthermore, when considering a summary judgment motion, this Court must view all evidence submitted in a light most favorable to the party opposing the motion. *See* Matsushita Elec. Indus. Co., Ltd. v. Zenith Radio Corp., 475 U.S. 574, 586, 106 S.Ct. 1348, 1356, 89 L.Ed.2d 538 (1986); Meyer v. Riegel Prods. Corp., 720 F.2d 303, 307 n. 2 (3d Cir.1983), *cert. dismissed*, 465 U.S. 1091, 104 S.Ct. 2144, 79 L.Ed.2d 910 (1984). Although the summary judgment hurdle is a difficult one to meet, it is by no means insurmountable.

Accordingly, in Celotex Corp. v. Catrett, 477 U.S. 317, 106 S.Ct. 2548, 91 L.Ed.2d 265 (1986), the Supreme Court concluded that "[o]ne of the principal purposes of the summary judgment rule is to isolate and dispose of factually unsupported claims or defenses, and we think it should be interpreted in a way that allows it to accomplish this purpose." Id. at 323-24, 106 S.Ct. at 2553.

# **B.** Summary Judgment in Patent Infringement Litigation

[1] The fact that this lawsuit involves a non-infringement analysis or the validity of a patent does not render this case unsuitable for disposition by summary judgment. Although patent infringement cases often raise complex factual issues, "the rules do not change simply because the case involves patent law." Aid Pack, Inc. v. Beecham, Inc., 641 F.Supp. 692, 694 (D.Mass.1986), *aff'd*, 826 F.2d 1071 (Fed.Cir.1987) (citing

D.M.I, Inc. v. Deere & Co., 755 F.2d 1570, 1573 (Fed.Cir.1985)). "Summary Judgment is appropriate in patent cases as in other cases under Rule 56(c)." Procter & Gamble Co. v. Nabisco Brands, Inc., 711 F.Supp. 759, 761 (D.Del.1989).

In fact, the Federal Circuit repeatedly has upheld the grant of summary judgment in patent infringement cases where there was no genuine issue of material fact. *See*, *e.g.*, George v. Honda Motor Co., Ltd., 802 F.2d 432, 434 (Fed.Cir.1986); Porter v. Farmers Supply Serv., Inc., 790 F.2d 882, 884 (Fed.Cir.1986); Brenner v. United States, 773 F.2d 306, 308 (Fed.Cir.1985); Builders Concrete, Inc. v. Bremerton Concrete Prods. Co., 757 F.2d 255, 257-58 (Fed.Cir.1985); Prodyne Enterprises, Inc. v. Julie Pomerantz, Inc., 743 F.2d 1581, 1583 (Fed.Cir.1984); Molinaro v. Fannon/Courier Corp., 745 F.2d 651, 654 (Fed.Cir.1984).

Thus, the Federal Circuit has advised: "[w]here no issue of material fact is present ... courts should not hesitate to avoid an unnecessary trial by proceeding under Fed.R.Civ.P. 56 without regard to the particular type of suit involved." Chore-Time Equip., Inc. v. Cumberland Corp., 713 F.2d 774, 778-79 (Fed.Cir.1983).

"In accordance with *Chore-Time*, it is incumbent on the trial judge to look beyond mere denials or arguments with respect to issues of scope and content of the prior art, differences between the prior art and the invention in suit, level of skill in the art or other factual issues." Union Carbide Corp. v. American Can Co., 724 F.2d 1567, 1571 (Fed.Cir.1984).

It is with these tenets in mind that the Court considers the defendants' summary judgment motions.

# **C.** Patent Infringement

[2] An infringement analysis requires two separate steps. First, the court must construe the claims asserted to be infringed as a matter of law in order to establish their meaning and scope. *See* Markman v. Westview Instruments, Inc., 517 U.S. 370, 116 S.Ct. 1384, 1393, 134 L.Ed.2d 577 (1996). Second, the claims as construed are then compared to the allegedly infringing device. *See id*. In this latter step, patent infringement may be found in either of two ways: literal infringement or infringement under the doctrine of equivalents.

# **1. Claim Construction**

[3] [4] Since Markman v. Westview Instruments, Inc., 52 F.3d 967 (Fed.Cir.1995), *aff'd*, 517 U.S. 370, 116 S.Ct. 1384, 134 L.Ed.2d 577 (1996), the interpretation of patent claim terms falls within the exclusive province of the Court. The standard to be applied for claim construction is what one of ordinary skill in the art at the time of the invention would have understood the term to mean. *See* id. at 986. The process is akin to statutory interpretation and must be viewed through the lens of objectivity with no inquiry as to the subjective intent of the inventor. *See* id. at 985-87. Thus, to ascertain the meaning of a patent claim a court should examine (1) the claims of the patent, (2) the specification, (3) the patent's prosecution history, and (4) extrinsic evidence. *See* id. at 979-81.

[5] The claims establish the limits or boundaries of the patent while the specification, of which the claims are a part, contains a written description of the invention that would enable one of ordinary skill in the art to make and use the invention. *See* id. at 979-80. "For claim construction purposes, the description may act as a sort of dictionary, which explains the invention and may define terms used in the claims." *Id*. (quoting In re Vogel, 422 F.2d 438, 441 (C.C.P.A.1970)). Indeed, a patentee can be his own lexicographer. *See* id. at 980 (citing Autogiro Co. of Am. v. United States, 181 Ct.Cl. 55, 384 F.2d 391, 396-98 (1967)). The written description, however, "does not delimit the right to exclude. That is the function and purpose of claims." *Id*.

[6] [7] Prosecution history is of primary significance to claim construction; it permits scrutiny of the

proceedings that occurred in the United States Patent and Trademark Office (the "Patent Office"). *See* id. at 980. "The court has broad power to look as a matter of law to the prosecution history of the patent in order to ascertain the true meaning of language used in the patent claims." *Id.* Yet, like the written description, the prosecution history cannot "enlarge, diminish, or vary" claim limitations. *Id.* (citing Goodyear Dental Vulcanite Co. v. Davis, 102 U.S. 222, 227, 26 L.Ed. 149 (1880); Intervet Am., Inc. v. Kee-Vet Labs. Inc., 887 F.2d 1050, 1054 (Fed.Cir.1989)).

[8] Lastly, extrinsic evidence through expert testimony lends understanding to the patent boundaries, but also may not vary or contradict the claims themselves. *See id.* at 980-81. "The court may, in its discretion, receive extrinsic evidence in order 'to aid the court in coming to a correct conclusion' as to the 'true meaning of the language employed' in the patent." *Id.* at 980 (quoting Seymour v. Osborne, 78 U.S. (11 Wall.) 516, 546, 20 L.Ed. 33 (1871)).

Upon consideration of the above, the Court must determine, as a matter of law, the meaning of the claim language at issue.

# 2. Literal Infringement

[9] Literal infringement occurs whenever a limitation of the patent is literally found in the accused device. *See* SmithKline Diagnostics, Inc. v. Helena Labs. Corp., 859 F.2d 878, 889 (Fed.Cir.1988). To literally infringe, the accused device must contain every limitation of the asserted claim. *See* Laitram Corp. v. Rexnord, Inc., 939 F.2d 1533, 1535 (Fed.Cir.1991).

# **3.** Doctrine of Equivalents

[10] Even if the accused device does not literally infringe, it may still infringe under the doctrine of equivalents "if there is 'equivalence' between the elements of the accused product or process and the claimed elements of the patented invention." Warner-Jenkinson Co., Inc. v. Hilton Davis Chem. Co., --- U.S. ---, ---, 117 S.Ct. 1040, 1045, 137 L.Ed.2d 146 (1997) (citing Graver Tank & Mfg. Co. v. Linde Air Prods. Co., 339 U.S. 605, 609, 70 S.Ct. 854, 856-57, 94 L.Ed. 1097 (1950)). In order for infringement to occur under the doctrine of equivalents, the accused device must perform substantially the same function in substantially the same way to achieve substantially the same overall result as the claimed invention. *See* Graver Tank & Mfg. Co., 339 U.S. at 608, 70 S.Ct. at 856; Pennwalt Corp. v. Durand-Wayland, Inc., 833 F.2d 931, 934 (Fed.Cir.1987), *cert. denied*, 485 U.S. 961, 108 S.Ct. 1226, 99 L.Ed.2d 426 (1988); *see also* International Visual Corp. v. Crown Metal Mfg. Co., Inc., 991 F.2d 768, 773-74 (Fed.Cir.1993) (Lourie, J., concurring) (quoting Graver Tank & Mfg. Co., 339 U.S. at 608, 70 S.Ct. at 856; Pennwalt S.Ct. at 856).

[11] Application of the doctrine of equivalents requires evaluating the equivalency of an element or part of the invention with one that is substituted in the accused product. Because each element contained in the patent claim is deemed material, the equivalency analysis must be directed to individual elements of the claim and not to the invention as a whole. As Justice Thomas pointed out in *Warner-Jenkinson*, whether equivalency is expressed in terms of the "triple identity" test focusing on function, way, and result, or is decided through an "insubstantial differences" analysis, is less important than whether the test is probative of the essential inquiry: "Does the accused product or process contain elements identical or equivalent to each claimed element of the patented invention?" 520 U.S. at ----, 117 S.Ct. at 1054. Thus, the determination of equivalence should be applied through an objective inquiry on an element-by-element basis at the time of infringement. *See id*.

[12] [13] Although equivalency under the doctrine of equivalents is a question of fact, it should not be employed to rewrite claims or to rescue the patentee's claim from a determination of non-infringement. Hence, application of the doctrine of equivalents is the exception and not the rule. *See* London v. Carson

Pirie Scott & Co., 946 F.2d 1534, 1538 (Fed.Cir.1991).

# **D.** Invalidity by Anticipation

A product is not patentable unless it is new. Determining whether a product is "new" within the meaning of the patent statute requires comparing the product with the products of the relevant prior art. *See* Shatterproof Glass Corp. v. Libbey-Owens Ford Co., 758 F.2d 613, 619 (Fed.Cir.), *cert. dismissed*, 474 U.S. 976, 106 S.Ct. 340, 88 L.Ed.2d 326 (1985). If a single piece of relevant prior art contains all the elements of the patent at issue, the prior art is said to have anticipated the patent. *See* Structural Rubber Prods. Co. v. Park Rubber Co., 749 F.2d 707, 715-16 (Fed.Cir.1984).

Under 35 U.S.C. s. 102(b), a patent is invalid as anticipated if the claimed invention:

was patented or described in a printed publication in this or a foreign country or in public use or on sale in this country, more than one year prior to the date of the application for patent in the United States.

Courts have interpreted s. 102(b) to require that "each and every element as set forth in the claim [be] found, either expressly or inherently described, in a single prior art reference." Constant v. Advanced Micro-Devices, Inc., 848 F.2d 1560, 1570 (Fed.Cir.), *cert. denied*, 488 U.S. 892, 109 S.Ct. 228, 102 L.Ed.2d 218 (1988); *see also* Minnesota Mining & Mfg. Co. v. Johnson and Johnson Orthopaedics, Inc., 976 F.2d 1559, 1565 (Fed.Cir.1992).

[14] [15] To determine whether a patent is anticipated by prior art under s. 102(b), the Court must undertake a three-step analysis. The first step is construction of the patent claims to determine their meaning in light of the specification and prosecution history. The second step requires the Court to compare the properly construed claims with the subject matter described in the prior art reference and identify the corresponding elements disclosed in the allegedly anticipating reference. *See* Titanium Metals Corp. of Am. v. Banner, 778 F.2d 775, 782 (Fed.Cir.1985). The third step requires the Court to determine whether the prior art reference is enabling, thereby placing the allegedly disclosed matter in the possession of the public. *See* Akzo N.V. v. United States Int'l Trade Comm'n, 808 F.2d 1471, 1479 (Fed.Cir.1986), *cert. denied*, 482 U.S. 909, 107 S.Ct. 2490, 96 L.Ed.2d 382 (1987). Accordingly, a prior art reference in a printed publication cannot anticipate an invention under s. 102(b) unless it enables one skilled in the art to produce the invention described in the patent.

[16] Defendants must prove anticipation by clear and convincing evidence. *See* Texas Instruments Inc. v. United States Int'l Trade Comm'n, 988 F.2d 1165, 1177 (Fed.Cir.1993) ("A patent is presumed valid and the party asserting invalidity must overcome this presumption by clear and convincing evidence establishing the facts which support the conclusion of invalidity.") (citing Intel Corp. v. United States Int'l Trade Comm'n, 946 F.2d 821, 834 (Fed.Cir.1991)); *see also* Dennison Mfg., Co. v. Panduit Corp., 475 U.S. 809, 810, 106 S.Ct. 1578, 1578-79, 89 L.Ed.2d 817 (1986).

### II. UNITED STATES PATENT NO. 4,097,899

# A. Background

United States Patent No. 4,097,899 (the " '899 patent"), was issued by the Patent Office on June 27, 1978. It is described as a Video Record Player Switching System. The alleged infringement centers on Claims 12, 13 and 14 of the '899 patent. Claims 13 and 14 are dependent on Claim 12. Claim 12 provides as follows:

12. Video record player apparatus comprising:

a player RF signal input terminal;

a player RF signal output terminal;

a player power supply developing supply potentials when selectively enabled;

means, rendered operative in response to supply potential development by said power supply, for forming a player output signal inclusive of picture carrier frequency oscillations and sound carrier frequency oscillations;

means, responsive to supply potential development by said player power supply, for establishing a first signal path between said output signal forming means and said player RF signal output terminal; said first signal path being disrupted in the absence of supply potential development by said player power supply; and

means, responsive to the absence of supply potential development by said player power supply, for establishing a second signal path between said player RF signal input terminal and said player RF signal output terminal; said second signal path being disrupted in the presence of supply potential development by said player power supply.

Roberge Cert. Ex. A at col. 9, line 62 to col. 10, line 18.

In lay terms, this patent claim discloses a radio frequency switch that directs RF FN5 signals from the video record player to the television receiver and at the same time blocks the flow of broadcast signals from the antenna to the television receiver. When the power to the video record player is off, the signal path from the antenna to the television experiences a low series impedance FN6 and is virtually unaffected; the signal from the antenna freely travels to the television. When the power to the video record player is on, the signal path from the antenna to the television receiver is disrupted by a high series impedance-an open electromechanical relay. FN7 Concurrent to the disrupt function is a bypass function, which diverts a substantial portion of the antenna television signal to ground. The bypass function is accomplished through the use of an energized diode. FN8 Hence, the '899 patent claims both a disrupt function and a bypass function, the former performed by an electro-mechanical relay, and the latter achieved through the use of an energized diode.

FN5. An RF signal is a signal in the radio frequency range.

FN6. In simplified terms, "impedance" can be understood as a measure of the degree of difficulty of passing current through a two terminal electric component. The higher the impedance of the component, the more difficult it is to pass current through that component.

FN7. An electro-mechanical relay acts like a signal bridge and reacts to a power supply. An open relay serves as a high series impedance because of the resulting physical gap in the signal path.

FN8. As used here, a diode is an electronic switch that is normally non-conductive to RF signals, or "off," but when a certain current flows through it, the diode becomes conductive to RF signals, or "on."

### 1. Function and Structure of the '899 Patent

The '899 patent is a means plus function patent. At column 10, lines 4-10, the video record player signal

path is designated as the first signal path, and at lines 11-17, the signal path between the antenna and the television receiver is referred to as the second signal path. *See* Roberge Cert. Ex. A at col. 10 lines 4-10 and 11-17.

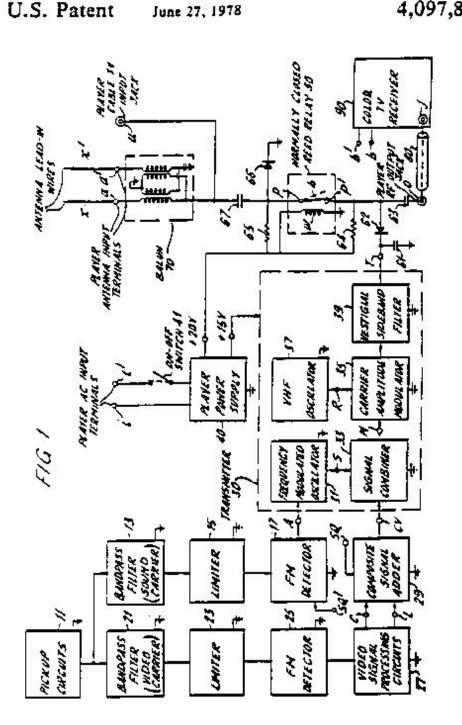

When the video player's power supply is on, each of the signal paths is affected simultaneously. First, the second signal path from the antenna to the television is disrupted through a high series impedance caused by the opening of the electro-mechanical relay, designated as relay (50) in the patent. *See* id. Ex. A, Fig. 1 ("App. 1").FN9 At the same time in the second signal path, diode (66) is energized and rendered conductive to permit a substantial portion of the antenna signal to be bypassed away from the antenna/television receiver signal path and sent to ground. *See* id. In the first signal path, video player RF signals, generated by transmitter (30), are sent through conductive diode (62) to the television receiver. Thus, when the video player power is on, the television receives only a signal from the video player, and the broadcast RF signals from the antenna are prevented from being transmitted to the television receiver. Also, because relay (50) is open, the video player RF signals are prevented from being transmitted to the antenna.

FN9. A diagram of the '899 patent is attached hereto as Appendix 1.

When the video player switch is in the off position, no RF signal is transmitted, diodes (62) and (66) are non-conductive, and relay (50) is closed. By this process, broadcast signals are transmitted from the antenna to the television receiver without disruption (nor are they bypassed to ground), while the first signal path between the video player and the television receiver is disrupted.

## 2. Nintendo's Denial of Infringement and Claim of Invalidity

Nintendo denies that its Nintendo Entertainment System ("NES") and Super Nintendo Entertainment System ("SNES") are covered by Claims 12-14 of the '899 patent. It asserts that these Nintendo systems employ an RF switch that is covered by Nintendo's U.S. Patent No. 4,745,478 (the " '478 patent") which is entitled "RF Switch" and was issued by the Patent Office on May 17, 1988. The '899 patent was not a cited reference in the '478 patent.

At the very outset, Nintendo contends that its switch does not contain a disrupt function and therefore cannot infringe the '899 patent literally or through the doctrine of equivalents. Moreover, Nintendo insists, the structure of its bypass function with respect to the antenna/television receiver path is significantly different. Apart from function and structure, Nintendo argues that its NES and SNES systems are not video record players and fall outside the claims of the '899 patent.

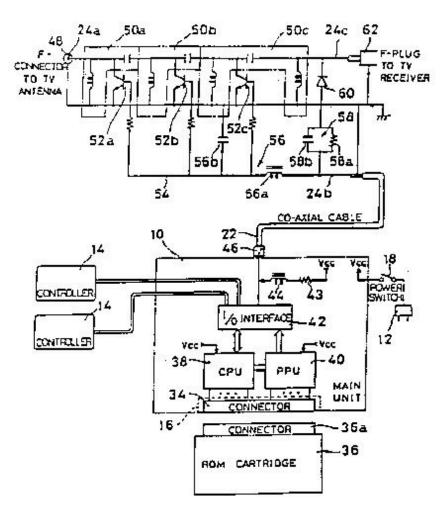

#### a. Nintendo's RF Switch

The RF switch used by Nintendo in its NES and SNES video game systems is the RF switch described in the '478 patent. Not unlike the '899 patent, the purpose of the RF switch in the '478 patent is to inhibit the antenna input of a television receiver when the television receiver is used as a monitor for a picture processing system, such as a personal computer, a video game system, or the like. *See* Roberge Cert. Ex. G, col. 1, lines 7-12; col. 1, lines 29-44. While the '899 patent speaks of first and second signal paths, the '478 patent describes the signal as a first television signal and a second television signal.FN10

FN10. In the '478 patent (and elsewhere in the documents relevant to this litigation), "TV" is often used to refer to television.

The Nintendo RF switch employs a system that primarily utilizes three-stage high-pass filters and three

switching transistors. *See* id. Ex. G, Fig. 2 ("App. 2") (denoting three-stage high-pass filters as 50a, 50b and 50c and three switching transistors as 52a, 52b and 52c).FN11 When the television receiver is used as a television receiver and not as a monitor, the first television signal from the television antenna is transmitted through the active three-stage filters to the television receiver. Under this scenario, the switching transistors remain off and the respective filters are not disabled. This electronic architecture permits the television signal from the television antenna to go to the receiver without interference.

FN11. A diagram of the '478 patent is attached hereto as Appendix 2.

Conversely, when the power switch to a game apparatus is turned on, the second television signal, also termed the "TV game signal," is applied to the television receiver which is used as a monitor. When this occurs, the first television signal is grounded and thereby automatically disabled. This happens because switching transistors 52a-52c are turned on and high-pass filters 50a-50c are disabled. Nintendo describes this as a "bypass" function with respect to the antenna/television path. Nintendo's Br. at 9.

Because Nintendo's RF switch does not place any disrupting component, such as an electro-mechanical relay, in the signal path between the antenna and the television receiver, Nintendo contends that the disrupt function of the '899 patent is lacking.

### b. Nintendo's Arguments in Support of the Lack of Equivalency Between the Function and Structure of the '899 Patent as Compared to the '478 Patent

Distinct from its lack of disruption non-infringement argument, Nintendo contends that Claim 12 of the '899 patent is a video record player apparatus containing an RF switch. Therefore, because of the "video record player" claim limitation, Nintendo reasons that its NES and SNES, characterized as video game systems, are not covered. Nintendo bottoms its argument by pointed references contained in the '899 patent. In column 1, lines 9-10, the video record player is described as an "apparatus for playback of a recording of picture representative video signals." Roberge Cert. Ex. A. An illustrative example of such a player system is a "video disc player" found at column 1, lines 15-16. Id. Moreover, Nintendo's expert, James K. Roberge, through his certification informs that a video disc player is completely passive in its operation; it does not generate any information itself and it does not alter the information contained in any of the signals it receives. *See* id. para. 43. Rather, it simply converts those signals to a format compatible with a television monitor. *See* id.

Noteworthy in Nintendo's analysis is the functional dissimilarity between Nintendo's video game systems and the video record player referenced in the '899 patent. Nintendo characterizes its systems as an "interactive" system, as opposed to a passive system, that solely retrieves stored information. By use of the term "interactive," Nintendo describes a system where the user is provided real time control over the images that are created. *See* id.

Another consideration advanced by Nintendo to contrast the '899 RF switch and the '478 RF switch is the latter's portability. Because Nintendo's RF switch can be moved away from the television and located with the user, it is free of the constraints that are inherent to the '899 RF switch, which is designed to be internal to the video record player. The '899 switch was designed for use with a stationary device that would sit atop or adjacent to the television monitor. Indeed, the inventor of the '899 RF switch, John Yu, never considered the portability of the switch or locating the switch outside the video record player. *See* Mascaro Cert. Ex. 3 at 29-30 and 60-65.

c. Nintendo's Invalidity Claim: Anticipation of the '899 Patent

Nintendo's invalidity claim is grounded on the theory that the '899 patent was anticipated by a Japanese patent application published more than one year prior to the filing date of the '899 patent application. More particularly, Nintendo asserts that a prior art reference filed with the Japanese Patent Office on behalf of Sharp Corporation, Patent Application SHO 49-7211 ("Sharp II") disclosed a switching operation that would have enabled one skilled in the art to produce the RF switch disclosed in the '899 patent.FN12 Because the claimed invention described in Sharp II preceded the '899 patent and was published more than one year in advance of the '899 patent's date of application for patent in the United States, Nintendo asserts that Sharp II anticipated, and therefore invalidates, the '899 patent.

FN12. Nintendo asserts that the '899 patent was anticipated by both Sharp II and a preceding Japanese patent application, No. 50-16919 ("Sharp I"). *See* Roberge Cert. para.para. 12-13, 44. Nintendo believes that both Sharp I and Sharp II disclose each of the elements of the '899 patent. Nintendo, however, has relied primarily on Sharp II as the invalidating prior art reference. *See* id. para. 46; Nintendo's Br. at 34-37. As such, the Court will focus its prior art discussion herein on Sharp II.

## 3. GE's Reply to Nintendo's Non-Infringement and Claim Construction Analysis

GE alleges both literal infringement and infringement through the doctrine of equivalents. Central to GE's argument is the premise that the '899 patent is a novel combination of RF switch and RF modulation. GE reasons that, under the '899 patent, when the power supply to the video record player is on, a "quieting feature" silences the television receiver's sound channel and turns the screen into a solid color. Conversely, when the video record player power supply is off, the television receiver's broadcast RF signals directly from the antenna, a function which serves to improve the television receiver's broadcast picture quality. GE further asserts that the disruption and bypass function of the '899 patent also solves the problem of signal leakage and eliminates interference with broadcast signals received by neighboring antennae. Lastly, GE disputes the narrow claim construction proffered by Nintendo that its NES and SNES entertainment systems are not video record players.

GE argues that the NES and SNES video game systems are, in fact, video record players. It disavows that use of the phrase "video record player," as set forth in the preamble to Claim 12, is a term of limitation. Similar to Nintendo, GE points to references in the patent description that it terms as the environment for the invention. GE maintains that the phrases "other video information services" found at column 1, lines 6-7, and "playback apparatus" used at column 2, line 30, are examples that demonstrate the breadth of the claim beyond a video record player. Lastly, GE portrays the NES and SNES systems as an apparatus for playback of a recording of picture representative signals. It avers that video and audio signals begin playing in a prearranged format as soon as the power to the NES or SNES system is turned on, not unlike the function of the '899 video record player. The Nintendo system is therefore passive, and becomes interactive only when the game controls are used; when the game controls are inactive, one could sit and watch the screen play prerecorded, changing scenes and pictures, including moving characters and background. *See* GE's Br. in Opp. at 28.

# 4. Expert Testimony

### a. Kurt Wallace for GE

Kurt Wallace ("Wallace") styles himself as a practicing engineer in the field of television-related electronics for more than thirty-five years. *See* Wallace Decl. para. 1. During this period of practice he has designed, developed and researched video recording and broadcast television equipment. *See* id. para. 2. After an examination of the '899 patent and its file history, the NES and SNES systems, and the '478 patent, Wallace concludes that the two Nintendo systems incorporate each of the elements of Claims 12, 13 and 14 of the '899 patent. *See* id. para. 4. Moreover, he concludes that neither the Sharp I nor the Sharp II patent

applications anticipated the '899 patent. See id. para. 5.

The first thirty paragraphs of the Wallace declaration explain the operation of the switching circuit disclosed in the '899 patent. This operation is defined in terms of impedance to ground, a relative concept whose application depends upon the presence or absence of a developed power supply voltage. In paragraph 31, Wallace summarizes the invention as follows:

When power supply voltage is not developed, the impedance between an antenna and the TV is low relative to the impedance to ground. Hence, the broadcast RF signals from the antenna are transmitted to the TV rather than to ground. When power supply voltage is developed, the impedance between the player and the TV is low relative to the impedance to ground. Also, the impedance between the antenna and television is high relative to the impedance to ground. As a result, the RF signals from the player are transmitted to the TV and the broadcast RF signals from the antenna are passed to ground.

See id. para. 31.

For purposes of the infringement analysis, Wallace examined the NES system's circuitry and observed its operation. He concludes that the NES system is a video record player because the RF modulator unit creates an RF output signal that is transmitted to the RF switch and permits the video and audio data to be converted into television signals from the player to be played on a television monitor. *See* id. para. 34. Wallace further concludes that the NES system incorporates an RF signal input and output terminal as claimed in elements (1) and (2) of the '899 patent. *See* id. para. 35. Wallace also concludes that the NES system incorporates a player power supply that is selectively enabled, as claimed in element (3) of the '899 patent. *See* id. para. 36.

The fourth element of the '899 patent provides for a "means, rendered operative in response to supply potential development by said power supply, for forming a player output signal inclusive of picture carrier frequency oscillations and sound carrier frequency oscillations." *See* Roberge Cert. Ex. A, col. 9, line 67 to col. 10, line 3. A comparison of the NES system and the circuitry described in the '899 patent is accomplished by Wallace in paragraph 41 of his declaration. By an examination of oscillation circuits, Wallace determines that the NES system incorporates the circuitry that forms an RF output signal to quiet the television, as claimed in element (4) of the '899 patent. *See* Wallace Decl. para. 41.

Elements (5) and (6) of the '899 patent establish first and second signal paths. The presence of either of these signal paths depends upon whether power to the video record player is on or off. Because Wallace determines that the NES system is a video record player, he finds that the NES system circuitry likewise includes two signal paths: "One signal path between the antenna and the TV is established whenever power to the NES player is absent. The other signal path between the player and the TV is established whenever power is applied to the NES player." *See* id. para. 42. Wallace describes the circuitry operation as follows:

The signal path between the NES player and the TV (the "first signal path" of claim 12) is established when power is applied to the NES as in the circuitry of the '899 patent. Also, when the signal path between the NES player and the TV is established, the signal path between the antenna and the TV (the "second signal path" of claim 12) is disrupted just like in the circuitry of the '899 patent. Disrupting the path between the antenna and the TV requires that television signals from the NES player are prevented from passing to the antenna and broadcast RF television signals from the antenna are prevented from passing to the TV. Further, when the power is not applied to the NES player, broadcast RF television signals pass to the TV but are prevented from passing to the NES player along the path between the NES player and the TV as in the circuitry of the '899 patent. Thus, the NES includes circuitry for establishing first and second paths in response to the development, or absence of, the power supply.

See id. para. 43.

Paragraph 46 of the Wallace affidavit is critical to the equivalency necessary for GE to sustain its '899 patent infringement argument against Nintendo. In that paragraph, Wallace confirms that when a power supply voltage is developed, the first signal path, the path between the NES player and the television, is established. At this time, Wallace asserts, the NES switching circuitry disrupts the second signal path, the path between the antenna and the television. Wallace concludes that the NES switching circuitry effectively bars RF signals from passing from the NES player to the antenna and also effectively bars broadcast television signals received at the antenna from passing to the television. *See* id. para. 46. This "effective bar" is illustrated in paragraphs 47 and 48 of his declaration and occurs as the result of the implementation of a combination of capacitors, resistors and transistors, whose interplay is defined in terms of high and low impedance. *See* id. para.para. 47-48.

In paragraphs 52-54, Wallace provides his analysis of the structure and interchangeableness of the switching circuitry found in both the NES system and the '899 patent. Because of the interconnected operation of the components of the NES system and the '899 patent, and the similarity that exists between them, Wallace reasons that a person of ordinary skill in the field of television-related electronics would find the circuitry of the NES RF switch to be functionally interchangeable with the switch circuitry of the '899 patent. Thus, he concludes, the NES system incorporates the circuitry of elements (5) and (6) of Claim 12 of the '899 patent. *See* id. para. 54.

Moreover, Wallace finds that the dependent claims of the '899 patent, Claims 13 and 14, are likewise present within the NES. *See* id. para.para. 55-56.

While Wallace devotes much of his declaration to an evaluation of the NES system and its circuitry, paragraphs 58 through 63 detail why he thinks all the elements of Claims 12, 13 and 14 of the '899 patent are also incorporated in the SNES system. Wallace indicates that he has observed the SNES system and has reviewed Katsuya Nakagawa's ("Nakagawa") certification.FN13 *See* id. para. 57. Following this review, Wallace avers that the RF switch in the SNES system is comprised of the same circuitry as the RF switch in the NES system and operates in the same fashion.

FN13. Nakagawa supervised the design of the RF switch used with both the NES and SNES systems. Nintendo included Nakagawa's certification as part of its written submissions.

### **b.** James Roberge for Nintendo

James Roberge ("Roberge") is a professor of electrical engineering at the Massachusetts Institute of Technology. He teaches and conducts research in the field of electronic circuits and their design. *See* Roberge Cert. para. 1. He has specific experience in the design of electronic circuits using frequencies in the RF range. *See* id. para. 2.

Professor Roberge studied the '899 patent, the '478 patent, Nakagawa's certification, and the deposition transcript and exhibits of John Yu ("Yu"), the named inventor of the '899 patent. *See* id. para. 4. At paragraph 5 of his certification, Professor Roberge concludes that Nintendo's NES and SNES systems do not infringe Claims 12-14 of the '899 patent. His conclusion of non-infringement is threefold:

1. The RF switch used in the NES and SNES does not perform the claimed function of disrupting the second signal path.

2. The structure described in the '899 patent for performing the claimed functions is not the same or

equivalent to the structure used in the Nintendo RF switch.

3. The NES and SNES are not "video record players" as required by claims 12 to 14 of the '899 patent.

See id. para. 5.

From paragraph 15 through paragraph 25 of his certification, Professor Roberge explains the function of the '899 patent when the video record player is in both the on and off position. Thereafter, in paragraphs 26 and 27, he explains the manner in which the Nintendo RF switch operates. Critical to its operation are three transistors,FN14 which are connected between the antenna-television signal path and ground. When the power to the NES or SNES is off, the three transistors are off; when the Nintendo systems are turned on, the transistors are likewise turned on. In the "on" position, the transistors provide three low impedance shunts to ground. Because the impedance of these shunts is low, Professor Roberge reasons that it is far easier for the antenna signal to travel down those additional paths to ground than to travel to the television receiver. *See* id. para. 26. Roberge states that, unlike the '899 patent, the Nintendo RF switch does not contain any component that creates a high series impedance, such as an electro-mechanical relay in the antenna to television signal path. *See* id. para. 27. With the Nintendo RF switch, a direct path always exists between the antenna and the television receiver.FN15

FN14. These transistors are used as electronic switches. They allow signals to flow when they are on and do not allow signals to flow when they are off.

FN15. The direct path is through three fixed value capacitors found in three high-pass filters. A capacitor is an electronic component that is conductive to RF signals but not conductive to DC signals. A fixed value capacitor is not a switching component. *See* Roberge Cert. para. 27 and n. 8.

Support for Professor Roberge's analysis that the Nintendo RF switch does not disrupt the signal path like the '899 patent, but instead redirects the signal (the bypass function) to ground, is contained in paragraphs 29 through 33 of his certification. In those paragraphs, Roberge explains that to disrupt a signal path by introducing a high series impedance is to break the path. On the other hand, to bypass a signal is to redirect that signal along an alternative path to another point. Hence, he concludes that in the realm of RF circuit art, disrupt and bypass are separate functions. When a signal path is broken, current flow stops. When a signal path is bypassed, the current flows away from the signal path but is not stopped. Because of this fundamental difference in RF circuit art, Roberge concludes, Nintendo's three transistors operate in a substantially different way from the electro-mechanical relay embodied in the '899 patent. *See* id. para. 32.

Moreover, Roberge asserts, the structure of the corresponding RF switches is significantly different. Nintendo's RF switch, as described in the '478 patent, is a purely electronic switch. In contrast, the electromechanical relay of the '899 patent relies on mechanical means to disrupt the signal path. Again Roberge avers that in the art of RF circuit design, a relay directly in the path that disrupts the path would not be considered equivalent to the Nintendo combination of switching components; the switching components are not placed directly in the antenna-television path, and they only bypass that signal path to ground. *See* id. para. 36.

In paragraph 43 of his certification, Professor Roberge distinguishes from a technical standpoint the difference between video record players and video game systems. He concludes that they are substantially different devices. Video record players contain electronic circuitry that allows them to play back pre-recorded signals for viewing on a television set. Video game systems, like the NES and SNES systems, contain picture processing units, other specialized chips, and digital logic circuitry that execute a game

program stored in a cartridge. When the video game system is activated, interactive images are generated on a television set as the user manipulates the controls of the game. If a user, for example, were to shoot an object displayed on the screen, the image on the screen would change. *See* id. para. 43.

## c. Katsuya Nakagawa for Nintendo

Nakagawa is one of the listed inventors of the RF switch which is described in the '478 patent. *See* Roberge Cert. Ex. G (copy of Patent Number 4,745,478 issued May 17, 1988). The '899 patent is not a cited reference for the '478 patent. By his certification, Nakagawa informs that he supervised the design of the RF switch used with both the NES and SNES home video game systems. *See* Nakagawa Cert. para. 1. This design was an RF switch which would be used to switch between the broadcast television signal received through the antenna and the video game system RF signals. *See* id. para. 2. Nakagawa acknowledges that the SNES system, Nintendo's second generation home video game system, uses the same RF switch as used in the NES system. *See* id. para. 3.

In paragraph 5 of his certification, Nakagawa voices his familiarity with the various RF switches that were already on the market when he began work on the Nintendo RF switch. Video tape recorders, for example, utilized an RF switch that was located inside the video tape recorder console. Video game RF switches, although located outside of the video game console, were still connected betweenthe console and the receiver and typically had to be operated manually. *See* id. para. 5.

Nakagawa wanted to design an RF switch that would be a separate device and that would be located outside of the video game console. *See* id. para. 6. By this design, he envisioned that players of the system, especially children, could move the video game console during use. Video tape recorders lack this flexibility of movement because the RF switch is located inside the video tape recorder console. *See* id. Moreover, with an external RF switch, the video game console can be readily disconnected without breaking the connection between the antenna and the television. Thus, a player may disconnect the console from one television set and connect it to another. *See* id. para. 7.

Another feature of the Nintendo RF switch specifically desired by Nakagawa was its automatic nature; Nakagawa sought to design the Nintendo RF switch to switch from the antenna to the video game whenever power for the video game was turned on. Conversely, when the power for the video game was turned off, Nakagawa wanted the RF switch to switch to the antenna. *See* id. para. 8. To accomplish this, Nakagawa designed the RF switch with all electronic components. He rejected the electro-mechanical relay approach because it was more expensive, required more power, and was less reliable than an electronic switch. *See* id. para. 10.

In paragraph 13 of his certification, Nakagawa catalogues his specifications for the Nintendo RF switch. They may be summarized as follows:

- -> The RF switch should be external and remote from the video game console.

- -> The RF switch should have the power and RF signals superimposed on a single wire.

- -> The RF switch should be all electronic.

- -> The RF switch should provide isolation when the video game is on.

-> The RF switch should pass the signal received by the antenna to the television with very little weakening of that signal when the video game is off.

-> The RF switch should not require power in order to operate when the video game is off.

-> The RF switch should have a low cost.

Id. para. 13.

The RF switch for the NES system uses a combination of high pass filters in the signal path between the antenna and the television. Nakagawa describes its operation as follows:

[W]hen the video game is off, the filters permit broadcast signals from the antenna to travel to the television receiver with very little signal loss. Three active switching components called transistors within the high pass filters are connected between the signal path and ground. When the video game is turned on the power is supplied to its three transistors, each of which creates a bypass between the signal path and ground. This shifts the cutoff frequency of the high pass filters to frequencies higher than channels 3 and 4 (the channels on which the video game is designed to operate), and an isolation of 65 decibels or higher is provided between the antenna and the television receiver at channels 3 and 4 when the video game is on.

Id. para. 15.

Additionally, Nakagawa rejected components that would actively provide isolation in the signal path between the antenna and the television receiver. *See* id. para. 16. He characterizes these type of components as unacceptable because they would have blocked or significantly weakened the signal received by the antenna when power to the video game was off. Instead, he opted for and used transistors as active components between the antenna television path and ground. By implementation of these transistors, he created isolation by changing the characteristics of the filters table by redirecting or bypassing the RF signal to ground. *See* id.

Nakagawa viewed his design as novel and was unaware of the RF switch disclosed in the '899 patent when he conceived, and subsequently patented, the '478 switch. *See* id. para.para. 17-18. After he read the '899 patent, Nakagawa concluded that the teaching of the relevant claims of the '899 patent would not have provided any assistance to him. In support of this statement, he sets forth three reasons, as follows:

1. In order to lower cost and achieve better reliability, I decided that the Nintendo RF switch should be designed to use all electronic components. In contrast, the '899 patent discloses an RF switch which uses an electromechanical relay switch. In general, electromechanical relays are more expensive and less reliable than electronic components.

2. I designed the Nintendo RF switch so that it has no electronic switching components in the signal path. Instead, three transistors redirect the signal to ground causing signals of the appropriate frequency to be bypassed, or redirected to ground. In contrast, the system disclosed in the '899 patent contains an electromechanical relay switch in the path between the antenna and the television set.

3. Because I wanted the Nintendo RF switch to be external and because I did not want to have a separate power line to the RF switch, I decided that Nintendo's switch should have both power and the RF signal superimposed on the same line. In contrast, the '899 patent describes an RF circuit which has separate lines for power and for the RF signal.

Id. para. 18.

In the closing paragraph of his certification, Nakagawa opines that "the '899 patent represents a fundamentally different RF switch design that functions in a substantially different way than the Nintendo

RF switch." Id. para. 19.

## **B.** Discussion

## 1. Non-infringement of Claim 12 of the '899 Patent

Nintendo contends that its NES and SNES systems neither literally infringe the '899 patent nor infringe the '899 patent pursuant to the doctrine of equivalents.

### a. Literal Infringement

To literally infringe independent Claim 12 of the '899 patent, every limitation of that claim must be found in Nintendo's accused devices. Claim 12 of the '899 patent is written in "means-plus-function" format. Such a format is provided by statute:

An element in a claim for a combination may be expressed as a means or step for performing a specified function without the recital of structure, material, or acts in support thereof, and *such claim shall be construed to cover the corresponding structure*, material, or acts *described in the specification and equivalents thereof*.

35 U.S.C. s. 112(6) (1984) (emphasis added).

At issue in this patent litigation is the last means-plus-function limitation of Claim 12. That limitation provides "means, responsive to the absence of supply potential development by said player power supply, for establishing a second signal path between said player RF signal input terminal and said player RF signal output terminal; said second signal path being disrupted in the presence of supply potential development by said player power supply." Roberge Cert. Ex. A at col. 10, lines 11-18.

The claimed function of "disrupting" the "second" signal path between the antenna and the television is provided for in the specification. *See id.* Ex. A at col. 1, lines 38-43; col. 4, lines 1-10. When the patentee acts as his own lexicographer, the specification of which the claims are a part may act as a sort of dictionary, which explain the invention and may define terms used in the claims. *See* Markman, 52 F.3d at 979-80. The '899 patent teaches that a signal path is "disrupted" by providing a high series impedance in that path. The second signal path, the path between the antenna and the television, is disrupted by the opening of an electro-mechanical relay. *See* App. 1 at relay (50). The "disrupting function" is separate and distinct from the bypass function performed by diode (66). *See* id. at diode (66).

The RF switch in the NES and SNES systems is a totally electronic switch. It employs a system that relies on the implementation of three-stage high-pass filters and three switching transistors. *See* App. 2 at filters 50a, 50b, and 50c and switching transistors 52a, 52b and 52c. When the television receiver is used as a receiver and not as a monitor, the three-stage filters are activated and permit the television signal to be transmitted from the antenna to the television receiver. At this time, the switching transistors remain off and the filters are not disabled. When the power switch to a NES or SNES system is activated, the switching transistors are energized, and the high-pass filters are disabled. Through this means, the television broadcast signal is bypassed to ground and automatically disabled.

[17] Because the '899 patent disrupts the broadcast television signal in the second signal path by means of an electro-mechanical relay and the Nintendo RF switch contains no switching components that disrupt the signal, the Nintendo RF switch cannot literally infringe the sixth element of Claim 12. *See* Roberge Cert. Ex. A at col. 10, lines 16-18 ("said second signal path being disrupted in the presence of ... power supply"). Nintendo's use of three transistors to redirect the signal to ground causes signals of the appropriate frequency to be bypassed. Consequently, Nintendo's electronic switching circuitry is not the same as or

equivalent to the electro-mechanical switching structure disclosed in the '899 patent.

The meaning and scope of the claims are clear and distinguishable. On comparison, the accused switch employed by Nintendo does not contain every limitation of the asserted claim. Without the presence of the disruption limitation as expressed in the sixth element of Claim 12, no literal infringement has occurred.

## **b.** Infringement Under the Doctrine of Equivalents

Beyond the reasons asserted to counter the allegation of literal infringement, Nintendo also contends that there has been no infringement under the doctrine of equivalents. Nintendo cites the disruption function of the '899 patent as a substantial difference between its RF switch and that of the '899 patent. Additionally, Nintendo asserts that the structure used to accomplish its RF switching is fundamentally different from the structure disclosed in the '899 patent-the Nintendo RF switch only bypasses; it does not conjointly disrupt and bypass.

[18] GE urges that under a function-way-result analysis, the performance of the Nintendo RF switch is the same as the patented device. *See* GE's Br. in Opp. at 29. GE is wrong.

Here, the critical inquiry is whether the accused product, the RF switch in the NES and SNES systems, contains elements identical or equivalent to each claimed element of the patented invention. Through an objective comparison conducted on an element-by-element basis at the time of infringement, the answer is resolutely one of non-infringement. Neither the function nor the structure of the '478 RF switch is identical or equivalent to the function and the structure of the '899 RF switch.

The '478 RF switch is an all-electronic switch that does not disrupt the television broadcast signal when the television receiver is used solely as a monitor. Through switching transistors, when energized, the television broadcast signal is bypassed to ground and automatically disabled. The '899 RF switch, when confronted with the same set of conditions, disrupts the television broadcast signal through the use of an electromechanical relay that creates a high level of impedance in the signal path between the antenna and television receiver. Additionally, a substantial portion of the antenna signal is bypassed to ground through diode (66). *See* App. 1 at diode (66). On an objective basis, a one-step electronic process that simply bypasses a signal is neither identical nor equivalent to a two-step process, employing an electro-mechanical device, that both bypasses and disrupts the signal.

GE argues through its expert, Wallace, that the switching circuitry found in both the NES and SNES systems are functionally interchangeable with that of the '899 patent. Wallace reasons that a person of ordinary skill in the field of television related electronics would deem Nintendo's capacitors equivalent to GE's electro-mechanical relay. Yet, capacitors are not switching components and are incapable of the disrupt function performedby the electro-mechanical relay. Instead, the switching function in the '478 patent results solely from bypassing the signal, which occurs when a lower impedance bypass to ground is introduced by a power supply to the video game system. With capacitors, a direct path always exists between the antenna and the television receiver; unlike the '899 circuitry, the direct path between the antenna and the television in the '478 circuitry does not include a high impedance switching device, such as an electro-mechanical relay, which actually disrupts the signal. The capacitors in the Nintendo switch only serve to block DC voltage and do not alter the impedance level, regardless of whether the power supply to the video game is turned on or off. Even Wallace, GE's own expert, admits that capacitors only transmit RF signals. *See* Wallace Decl. para. 19. With respect to the direct path between the antenna and the television, the capacitors in the '478 patent are not equivalent to the electro-mechanical relay in the '899 patent.

The most telling evidence of the lack of equivalence or interchangeableness between the structures of the '478 RF switch and the '899 RF switch is the testimony of the '899 patent's inventor, Yu. Yu's testimony is

recited in Nintendo's memorandum in support of summary judgment at pages 12-13. In its pertinent part, it reads as follows:

During the development of the RF switch structure disclosed in the '899 patent, the named inventor, John Yu, initially designed a structure that included four electro-mechanical relays. Patent Disclosure Form at GE 000101; Yu Tr. at 102 (*see* Mas. Cert., Exs. 2 and 3). Over a period of several months, Mr. Yu continued to work on the design of his RF switch in order to eliminate as many of the electro-mechanical relays as possible. Yu Notebook at GE 003111-12, 003121-22; Yu Tr. at 117, 119-121 (*see* Mas. Cert., Exs. 4 and 3). He did this because he recognized that electro-mechanical relays were not as reliable as electronic switching components. Yu Tr. at 116-117, 119-120 (*see* Mas. Cert., Ex. 3). [footnote 10: In fact, in another part of the device that Yu was working on, he decided to replace an electro-mechanical relay with an electronic switch specifically in order to "increase reliability and to reduce the cost." Yu Notebook at GE 003129 (*See* Mas. Cert., Ex. 4).]

Ultimately, Mr. Yu tried to design an RF switch structure which was all-electronic and included no electromechanical relays. However, he was unable to do so. Yu Tr. at 163-165 (*see* Mas. Cert., Ex. 3). When Mr. Yu placed an electronic switching component directly in the antenna/television signal path in order to be able to disrupt that path, it caused an unacceptable loss of antenna signal strength when the power was 'off.' Yu Notebook at GE 003121; Yu Tr. at 144-45, 163-165 (*see* Mas. Cert., Exs. 4 and 3). As a result, Mr. Yu ultimately settled on an RF switch structure which used one electro-mechanical relay in the antenna/television signal path that physically opened and closed the path, and disclosed this structure as the only embodiment in the '899 patent. Yu Memorandum at GE000099; '899 patent, Figure 1 (*see* Mas. Cert., Ex. 5; Rob. Cert., Ex. A). He never designed an acceptable switch that performed its switching function by only bypassing the antenna/television path when the VTR was turned on. Yu Tr. at 138-39 (*See* Mas. Cert., Ex. 3); Rob. Cert. para. 33.

Nintendo's Br. at 12-13.

Logic compels the decision that these RF switches are not structurally identical or equivalent. Certainly, if Yu was unable to design an all-electronic switch sufficiently appropriate to perform the disrupt function, it necessarily follows that a person of ordinary skill in the field of television-related electronics would likewise be unsuccessful.

Beyond the missing disruption function and Nintendo's all-electronic RF switch, other differences counsel against a finding of equivalence between the two devices.

The RF switch disclosed in the '899 patent is a switching system to be used in a video record player. Despite a fervent attempt to categorize the NES and SNES systems as video record players, such effort is unavailing to GE. These Nintendo systems are not merely an "apparatus for playback of a recording of picture representative video signals" as discussed in the '899 patent. Roberge Cert. Ex. A at col. 1, lines 9-10. These video games are interactive and each scene is generated in real-time in response to input from the game player. They do more than simply play back a pre-recorded series of video signals. The video record player, in contrast, is passive in nature, and the specification does not contemplate that the '899 RF switch would have any application in any other system or environment. *See* Nintendo's Br. at 26.

Although GE points to language contained in the specification to demonstrate that the scope of the invention exceeds video record player systems and includes "other video information sources," *see* Roberge Cert. Ex. A, col. 1, line 4, such a vague reference is not sufficient to ensure systems that were not within the contemplation of the inventor. By contrast, Nakagawa in the '478 patent enumerates picture processing systems such as a personal computer, a video game, or the like. *See* Roberge Cert. Ex. G at col. 1, lines 10-12. Because the '899 RF switch was designed for video record players, the claims at issue should be limited

to that device and not expanded through vague and uninformative language. This is especially true in a crowded art field. As stated in Exxon Chemical Patents, Inc. v. Lubrizol Corp., 64 F.3d 1553, 1563 (Fed.Cir.1995) (Plager, Jr., concurring), *cert. denied*, 518 U.S. 1020, 116 S.Ct. 2554, 135 L.Ed.2d 1073 (1996):

[W]e are not free to read the claims as they might have been drafted, even if as drafted they do not accomplish what the inventor may have intended.

Claim drafting is itself an art, an art on which the entire patent system today depends. The language through which claims are expressed is not a nose of wax to be pushed and shoved into a form that pleases and that produces a particular result a court may desire. The public generally, and in particular, the patentee's competitors, are entitled to clear and specific notice of what the inventor claims as his invention. That is not an easy assignment for those who draft claims, but the law requires it, and our duty demands that we enforce the requirement. There is no room in patent claim interpretation for the equivalent of the *cy pres* doctrine; that would leave the claiming process too indefinite to serve the purposes which lie at the heart of the patent system.

Other differences between the switches demonstrate the lack of identity or equivalence between them. For example, Nakagawa, the inventor of the '478 switch, implemented a design concept that permitted the RF switch to be located outside of the video game console. Unlike RF switches that are located inside a video tape recorder, Nakagawa's RF switch provides portability during use. Moreover, with an external RF switch, the video game console can be readily disconnected without breaking the connection between the antenna and the television. Therefore, a player may disconnect the console from one television set and connect it to another. The '899 RF switch does not permit the choice and convenience of movement. *See* Nakagawa Cert. para. 7.

Seemingly insignificant, but of structural importance, was Nakagawa's decision to eliminate a separate power line to the '478 RF switch. In contrast to the '899 patent, which describes an RF circuit with separate lines for power and for the RF signal, Nakagawa decided that Nintendo's switch should have both power and the RF signal superimposed in the same line. His '478 patent accomplished that goal.

To return to where the analysis began, the Court concludes that there is no infringement under the doctrine of equivalents and Nintendo's summary judgment of non-infringement as to Claim 12 must be granted.

# 2. Non-infringement of Claims 13 and 14 of the '899 Patent

Because the Court has determined that Claim 12 has not been infringed literally or under the doctrine of equivalents, dependent Claims 13 and 14 are likewise not infringed and will be included within the Court's grant of summary judgment in favor of Nintendo.

# 3. Claims 12-14 of the '899 Patent Are Invalid